如何减少芯片在运输过程中的损坏率

半导体芯片(如集成电路、晶圆)在运输过程中易受机械冲击、静电放电(ESD)、温度/湿度波动、化学污染等因素影响,导致损坏率高达5-10%。通过优化包装、环境控制和物流管理,可将损坏率降低至1%以下。以下基于行业最佳实践(如JEDEC标准和ESD协会指南),总结关键措施。实施时,建议与专业物流伙伴(如Dimerco)合作,并进行风险评估。

主要损坏原因及预防原则

- 机械冲击/振动:运输颠簸导致芯片裂纹或断裂。

- 静电放电(ESD):低至3V的静电即可损坏薄栅氧化层。

- 环境因素:高温/低温、湿度导致变形或腐蚀。

- 化学污染:包装材料出气或污染物接触芯片。

具体措施:采取步骤减少损坏风险

以下是分阶段的操作指南,按运输流程排序。每个措施包括实施要点、益处及注意事项。

| 阶段 | 措施 | 实施要点 | 益处 | 注意事项 |

|---|---|---|---|---|

| 准备阶段(包装前) | 选择专用芯片托盘和材料 | 使用JEDEC标准托盘或IC托盘(材料如PS、PP或PAS,低吸水率≤0.2%);添加抗静电涂层(电阻率10^6-10^9 Ω)。 | 物理隔离芯片,防碰撞/刮擦;阻挡静电传导。 | 确保托盘可回收,减少成本;测试水吸收率以防湿度变形。 |

| 包装阶段 | 采用多层缓冲保护 | 芯片置于ESD安全塑料托盘内,填充抗静电聚氨酯泡沫或硅支架;外层用真空密封袋+硬壳箱。 | 吸收振动,防止移动;降低ESD风险达90%。 | 避免标准包装(如纸箱),易导致化学出气污染。 |

| 环境控制阶段 | 监控温度与湿度 | 运输容器内保持20-25°C、相对湿度40-60%;使用温湿度记录仪。 | 防止热应力或潮湿腐蚀,延长芯片寿命。 | 对于敏感芯片(如MOSFET),选用辐射屏蔽设计。 |

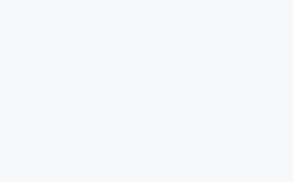

| 运输阶段 | 优化物流路径与模式 | 优先空运或专用陆运,缩短时间(<48小时);使用振动减震车辆,避免频繁转运。 | 减少机械应力,降低损坏率至<1%。 | 选择有半导体经验的物流商,确保全程追踪。 |

| 人员与设备阶段 | 实施ESD防护培训 | 操作员戴防静电腕带,使用接地工作站;设备(如机器人臂)接地。 | 消除人为静电源,减少场返回故障。 | 定期培训,覆盖从工厂到现场的全链条。 |

| 验收与测试阶段 | 运输后快速检验 | 到货后立即检查外观、ESD测试(HBM 2kV标准)和功能验证。 | 及早发现隐蔽损坏(如微裂纹),降低下游损失。 | 若抽样检验,覆盖10%批次;记录数据优化下次运输。 |

实施建议

- 成本效益:初始投资(如专用托盘)可回收,通过减少报废率(平均节省5-15%)在6个月内回本。

- 法规合规:遵循IATA危险品规则(虽芯片非危险品,但ESD类似)和中国《半导体行业标准》(GB/T )。对于国际运输,参考欧盟Chips Act的ESD预防指南。

- 案例:半导体企业采用jig托盘后,运输损坏率从8%降至0.5%,并缩短交货周期。

通过以上措施,可系统性降低风险。如果您的芯片类型(如晶圆或封装IC)或运输距离具体,可提供详情进一步定制方案。